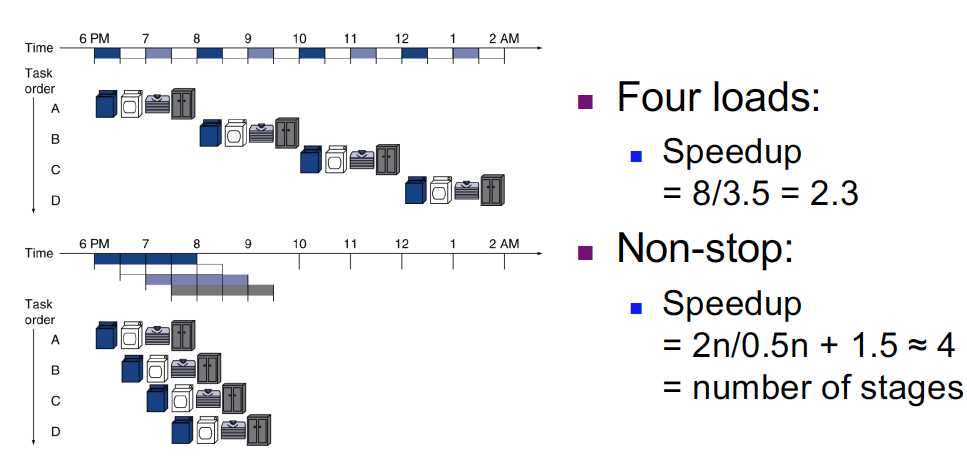

Pipelining

여러 명령어가 중첩되어 실행되는 구현 기술

Five Stages of Instruction

- IF : 메모리에서 인스트럭션 패치

- ID : 인스트럭션 해독 및 레지스터 읽기

- EX : 연산 수행 및 주소 계산

- MEM : 메모리 읽기/쓰기

- WB : 레지스터에 쓰기

Hazards

다음 사이클에 실행되어야 할 인스트럭션이 실행될 수 없는 상황을 Hazard라고 한다.

- Structure Hazards : 같은 클럭 사이클에 실행하기를 원하는 명령어의 조합을 하드웨어가 지원할 수 없기 때문에 발생 ex) IF와 MEM

- Data Hazards : 어떤 단계가 다른 단계가 끝나기를 기다려야 하기 때문에 파이프라인이 지연되어야 하는 경우 발생

- Control Hazards : 다른 명령어들이 실행되는 동안 어떤 명령어의 결과에 기반을 둔 결정을 할 필요가 있을 때 발생 ex) branch

Structure Hazards

load/store는 메모리에서 데이터에 접근하고, 메모리에서 instruction을 패치하기도 한다. 파이프라인에 메모리가 하나라면 같은 메모리에서 데이터 접근과 IF가 동시에 발생하여 충돌이 일어나거나 해당 사이클을 stall시키는 bubble이 발생할 수 있다. 따라서 파이프라이닝 된 데이터패스는 분리된 인스트럭션/데이터 메모리를 필요로한다.

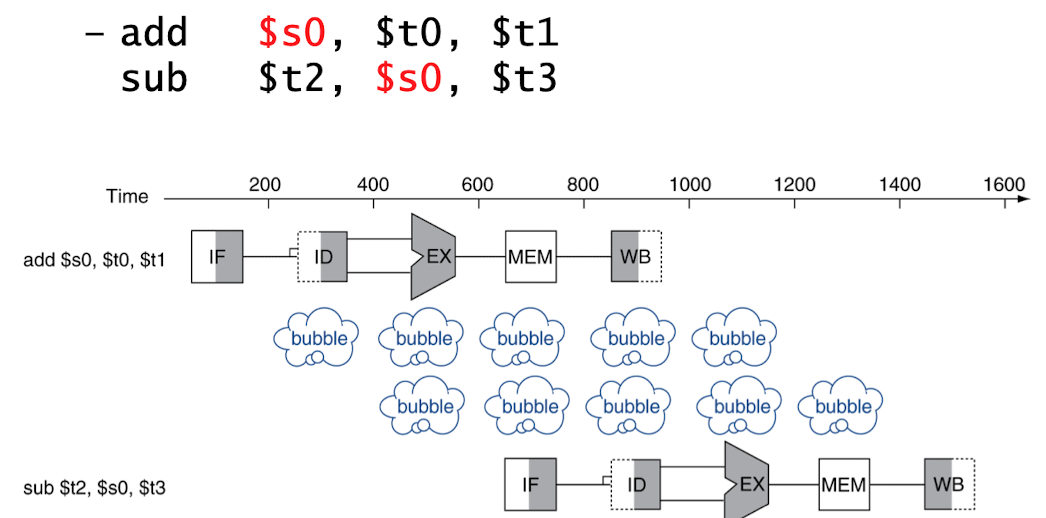

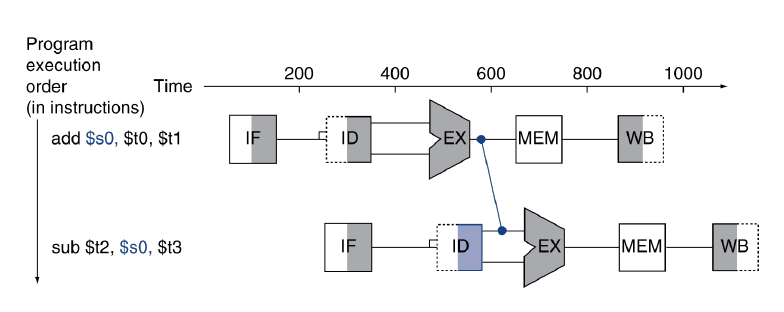

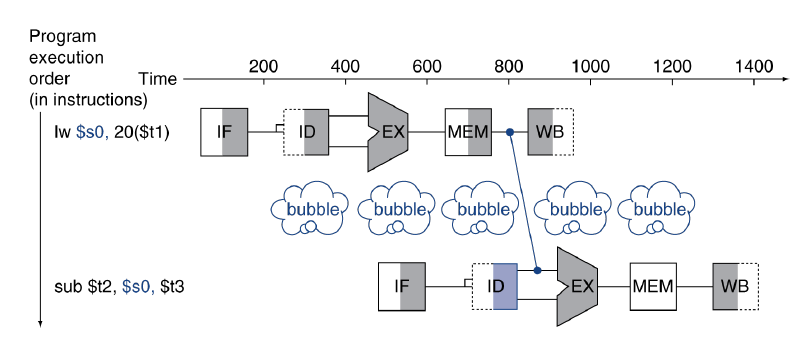

Data Hazards

- Forwarding

이와 같이 앞에서 계산된 결과를 뒤에서 바로 사용해야할 때 데이터 해저드가 파이프라인을 심각하게 지연시킬 수 있다. 이를 해결하기 위해 별도의 하드웨어를 추가하여 정상적으로 얻을 수 없는 값을 내부 자원으로 부터 일찍 받아 오는 것을 Forwarding 또는 Bypassing이라고 한다.

먼저 실행된 명령어가 끝나지 않더라도 필요한 값이 계산되는 대로 일찍 가져와서 다음 인스트럭션에서 사용한다.

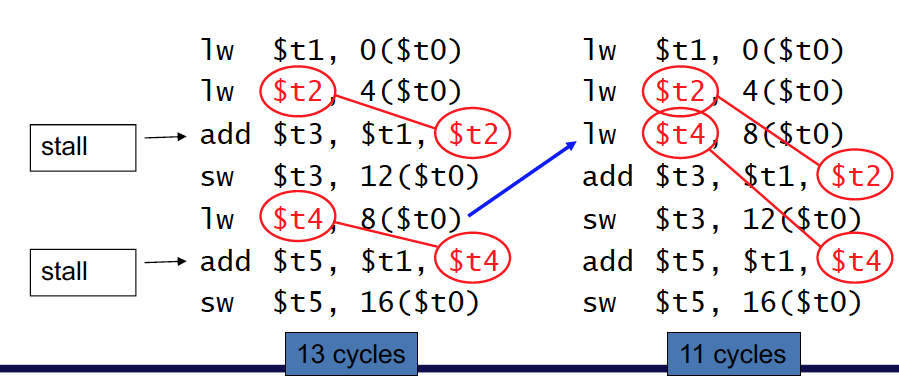

- Load-Use Data Hazard

load된 것을 다음 인스트럭션에서 바로 급하게 사용하려면 위와같이 stall이 발생하지 않을 수 없다. 이러한 상황에는 load된 것을 나중에 사용해서 굳이 stall이 일어나지 않게 하는 방식으로 인스트럭션의 순서를 조정한다.

Control Hazards

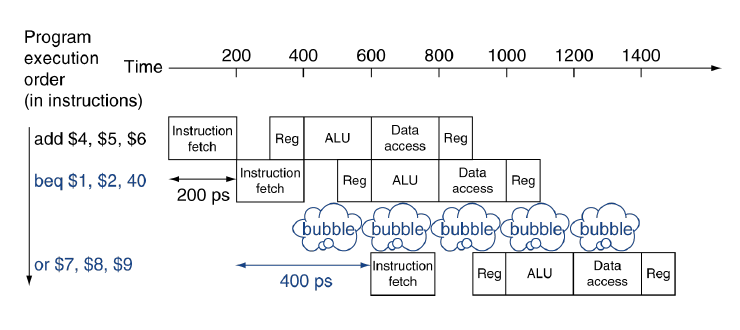

- Stall on Branch (분기 시 지연)

분기 명령어가 나올 때 마다 분기 결과를 확인하고 다음 인스트럭션을 패치하느라 다음 인스트럭션 수행이 지연이 된다면 큰 속도 저하를 초래할 것이다. 좀 더 효율적으로 분기 명령어를 다루기 위해서 컴퓨터는 예측을 사용한다. 가장 간단한 방법으로는 분기는 항상 실패한다고 예측하는 것이다.

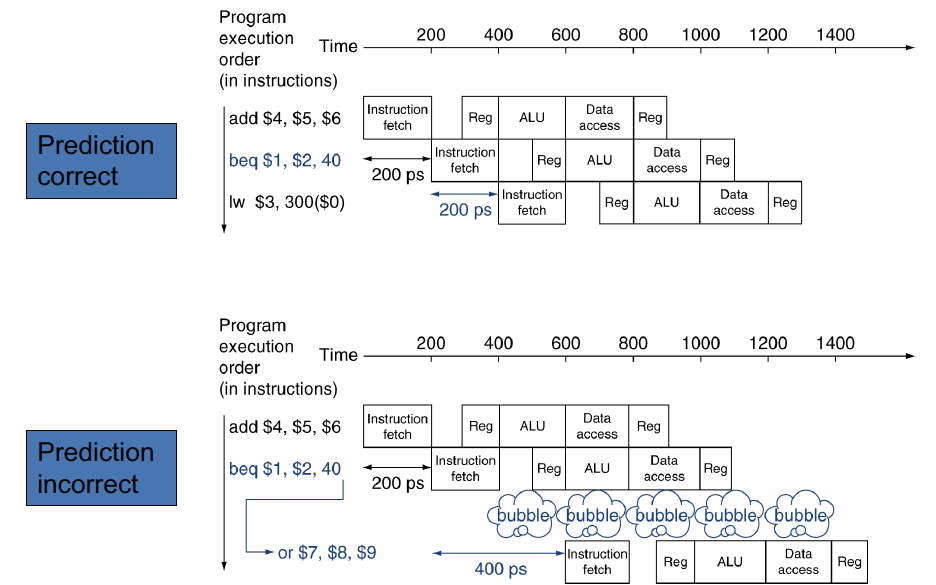

- Branch Prediction

분기가 실패한다고 예측했을 때 그 예측이 적중한다면 일반적인 명령어 수행 속도와 같이 다음 인스트럭션이 수행 되고, 그 예측이 빗나갈 때만 다음 인스트럭션 패치를 위한 지연이 발생한다.

'Computer Science > Computer Architecture' 카테고리의 다른 글

| [Computer Architecture] Cache Memory (캐시 메모리) (0) | 2024.08.06 |

|---|---|

| [Computer Architecture] CPU Datapath (CPU 데이터패스) (0) | 2024.07.28 |

| [Computer Architecture] Floating Point (부동 소수점) (0) | 2024.07.16 |

| [Computer Architecture] Integer Arithmetic (정수 연산) (0) | 2024.07.11 |

| [Computer Architecture] CPU Operation (CPU 작동 원리) (0) | 2024.07.07 |